5-Microstep Drive. Xilinx CPLD

А можно это в Алтеру перекомпилять ?

ЛЕГКО!

ЛЕГКО!

Насколько я помню, Марисс там активно использует выходы с открытым коллектором. В дешевых Альтерах они тоже есть?

P.S. Я то сам так и не сподобился двинуться дальше баловства, суета сует…

Насколько я помню, Марисс там активно использует выходы с открытым коллектором. В дешевых Альтерах они тоже есть?

А кто мешает верхний транзистор закрыть ПОСТОЯННО?

Чего там нет, так это триггера шмидта по входу, но генераторы и на простых входах стабильно работают.

ЛЕГКО!

Пожалуйста. Просто Алтер на списанных\дохлых платах завались. а Ксилинков обыскался.

А кто мешает верхний транзистор закрыть ПОСТОЯННО?

Чего там нет, так это триггера шмидта по входу, но генераторы и на простых входах стабильно работают.

Юрий, Вы на этом деле стаю собак уже съели 😃, а для меня это новость, что можно раздельно управлять плечами выходного каскада.

Там есть даже “примитив” opndrn - сам все делает, но если есть желание то можно и по отдельности транзисторами “рулить”.

А вообще CoolRuner это классическая Альтеровская PLD-ха.

В 90-х Альтера продала свою технологию Филипсу, те ,надо отдать должное, здорово снизили потребление, но продукт массовости не получил.

Xilinx же PLD так и не научился делать( хотя с FPGA у него все нормально) просто перекупает все подразделение, и теперь делает нормальные PLD как и Альтера.

P.S. CoolRuner - Филипсовское название.

Примерно так. Осталось запаять пару перемычек и прошить CPLD. И можно тестировать.

ждем с нетерпением тестов…

В лоб не прокомпилилась, там используется Ксайлинкоская либа, но у Альтеры есть аналогичная - попробую ее прикрутить.

Похоже дело в распиновке ног на OSCA, OSCB и CLK. Разместил ноги:

CLK - P1

OSCA - P42

OSCB - P2

Теперь ругается только на CLK и похоже требует чтобы я ей схему включения CLK нарисовал.

Cpld - Inferring BUFG constraint for signal ‘CLK’ based upon the LOC constraint ‘P1’. It is recommended that you declare this BUFG explicitedly in your design. Note that for certain device families the output of a BUFG constraint can not drive a gated clock, and the BUFG constraint will be ignored.

В общем дело в распиновке. Читаю документацию.

Этот пип ПЛД требует подключения CLK на выделенный (по доке) пин - нуна назначить на него и подключить входной буффер.

Ну и какой это пин и как подключить входной буффер?

Спаял сегодня программатор. Пока сверлил плату сломал два сверла 😦 Грустно.

Перенес в проекте OSCA с 44 на 42 ногу (CLK и OSCB остались на старых 2 и 43) и все ошибки ушли. Подключил праграмматор через LPT кабель. Провозился с пару часов но так законнектится к CPLD не смог. Все проверил, даже саму CPLD на другую перепаял, не помогло. Потом выяснил что по умолчанию iMPACT использует Parallel Cable IV а у меня III. Поменял настройки, не помогло. Выкинул нахрен кабель и воткнул программатор напрямую в LPT порт. Все заработало как часы. Значит надо поиграться с входными сопротивлениями в программаторе.

CPLD прошилась быстро и после перегрузки питания получил красивые ипмульсы CLK (OSCB-).

Теперь вторая проблемма. Моя покупная плата опторазвязки наотрез отказывается работать с частотами сигналов STEP. DIR проходит а ШАГ проскочить не успевает. Оптопары стоят 817D. На самом драйвере опторазвязка отсутствует, а напрямую в LPT порт (даже для теста) подсоединять что-то страшновато. Придется завтра паять опторазвязку на HCPL2631.

при использовании Мача можно инвертануть сигнал степ - полегчает.

тут подробно с картинками как настроить мач kosmodrom.com.ua/data/cncstepdriver/cnccall.php

Инвертнул степ, действительно полегчало. Заодно и в программе CPLD пришлось степ проинвертировать. Еще слегка промучался с уровнями входных сигналов. Между платой опторазвязки и входами драйвера воткнул последовательно по диоду. Теперь хоть сигналы красиво до входа cpld доходят. На выходах стоит меандр. Пока все работает как надо. Время подключать двигатель и смотреть откуда дым повалит. Шучу, но надо приготовиться.

Подсоеденил мотор, дал для начала 24В питания. Ограничил ток до 1А (внешний резистор на установку ограничения тока работает как надо. 1к эквивалентен 1А) Все заработало. Крутится во все стороны. Добавил скорости. Пищать стал меньше. Руками вал не остановить. Не совсем понятно работает-ли ограничение тока при остановке двигателя. Этим попозже займусь.

На данный момент драй работает намного приятней чем то что делал на LS7290. Наверно потому что микростеп работает.

Согласно формуле Марисса по расчету необходимого напряжения питания получается что моему мотору нужно 59В.

Индуктивность обмотки 3.4 mH, квадратный корень из 3.4 * на 32 = 59В.

Подсоеденил блок питания на 48В. Что тут началось. Компьютер аж запищал. Клавиатура стала выдавать непонятно что. Mach крутит взад-вперед невзирая на положение клавиш. Видно помехи валят ну очень сильные. Заэкранировал провода от мотора, слегка помогло но не до конца. Наверно и сам мотор надо на землю сажать. Пока буду крутить от 24В. Выходные транзисторы на радиаторы не цеплял, а они и не греются.

В целом впечатления хорошие. Теперь надо еще 3 драйва собрать и пробовать на станке. Уже должно быть быстрее.

Схему как файл прикреплять уже нельзя. Кому надо текущий вариант схемы берем тут.

Придется завтра паять опторазвязку на HCPL2631.

Вы решили вопрос опторазвязки ?

если да - выложите пож. схему и каковы результаты…

заранее благодарен

(сам бьюсь с этой проблемой - rcopen.com/forum/f110/topic123955/372 - может что дельное подскажите)

В качестве опторазвязки покупная плата. Еще весной на eBay купил. Её описание есть тут: rcopen.com/forum/f110/topic145874. Там стандартное включение оптопары 817D. Поскольку в Mach стоит активный уровень “0” то я пустил сигналы от оптопары через последовательно включенный диод на вход драйва, катод диода к оптопаре а анод к драйву. Теперь “0” с оптопары через диод шунтирует вход драйва. А 5В с опторазвязки запираются диодом и не портят мне 3.3В на входе cpld. Теперь моя “1” приходит от 3.3В питания cpld а “0” (точнее 0.6В, падение напрядения на диоде) за счет шунтирования входа.

В самом Mach в настройках двигателя выставил длительность импульсов 15ms, хотел 25 поставить, но Mach не дал это сделать.

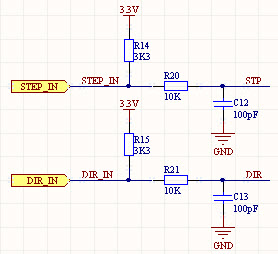

Вот моя входная схема Step and Dir.

Даже с диодами она поначалу работать не хотела, увеличил номиналы подтягтвающих резисторов с 3.3к до 6.8к и тогда заработало. Похоже что у этих оптопар нагрузочные токи никакие. Одним словом развязку надо делать на HCPL2631. Тогда все работает как надо без всяких танцев с бубном.

Это я потом соберу. Для начала хватит того что есть.

Я не совсем понял в чем именно у вас проблеммы с опторазвязкой.

В лоб не прокомпилилась, там используется Ксайлинкоская либа, но у Альтеры есть аналогичная - попробую ее прикрутить.

Получилось или нет ?

В процессе…

НЕМНОГО теории Верилога, и присланный проект компилится без ошибок.

Лег в EPM3064, занял 64% - как будет работать посмотрим на праздниках.