5-Microstep Drive. Xilinx CPLD

impact должна называться

хотя может еще как то переименовали

www.xilinx.com/support/…/xapp069.pdf

Народ, приветик.

Вижу, многие мучаются с программированием Xilinx. Я в свое время тоже разбирался в этой проблеме, так что делюсь своим опытом. Просмотрите приложенный файл - это часть выполненного курсовика по Verilog, железо от Digilent - тестовая плата со Спартаном-3. Курсовик выполнен как пошаговая инструкция по программированию.

Народ, приветик.

Просмотрите приложенный файл

Ну и куда смотреть? Где файл потерялся?

файл с описанием

CPLD Xilinx CoolrunnerII, XC2C64-7VQ44C

После компиляции проекта выходит два предупреждения:

[Warning]:INFO:Cpld - Inferring BUFG constraint for signal ‘CLK’ based upon the LOC constraint ‘P43’. It is recommended that you declare this BUFG explicitedly in your design. Note that for certain device families the output of a BUFG constraint can not drive a gated clock, and the BUFG constraint will be ignored.INFO:Cpld - Inferring BUFG constraint for signal ‘OSCA’ based upon the LOC constraint ‘P44’. It is recommended that you declare this BUFG explicitedly in your design. Note that for certain device families the output of a BUFG constraint can not drive a gated clock, and the BUFG constraint will be ignored.

[Warning]:Cpld:1239 - The global clock designation (BUFG) on signal ‘OSCA_IBUF’ is ignored. Most likely the signal is gated and therefore cannot be used as a global control signal.

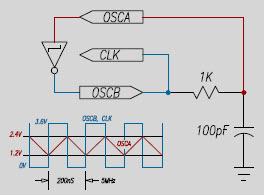

Схема внешнего генератора простая:

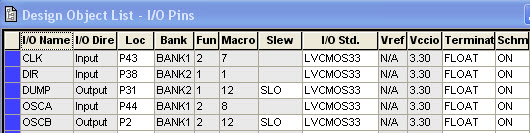

Соответственно ноги в Floorplan IO

Строка в Verilog описывающая эту функцию: assign OSCB = ~OSCA;

Что это за BUFG constraint и где ее надо правильно описать?

Пришли проект, попробую в Максе-Квартусе откомпилить.

А можно это в Алтеру перекомпилять ?

А можно это в Алтеру перекомпилять ?

ЛЕГКО!

ЛЕГКО!

Насколько я помню, Марисс там активно использует выходы с открытым коллектором. В дешевых Альтерах они тоже есть?

P.S. Я то сам так и не сподобился двинуться дальше баловства, суета сует…

Насколько я помню, Марисс там активно использует выходы с открытым коллектором. В дешевых Альтерах они тоже есть?

А кто мешает верхний транзистор закрыть ПОСТОЯННО?

Чего там нет, так это триггера шмидта по входу, но генераторы и на простых входах стабильно работают.

ЛЕГКО!

Пожалуйста. Просто Алтер на списанных\дохлых платах завались. а Ксилинков обыскался.

А кто мешает верхний транзистор закрыть ПОСТОЯННО?

Чего там нет, так это триггера шмидта по входу, но генераторы и на простых входах стабильно работают.

Юрий, Вы на этом деле стаю собак уже съели 😃, а для меня это новость, что можно раздельно управлять плечами выходного каскада.

Там есть даже “примитив” opndrn - сам все делает, но если есть желание то можно и по отдельности транзисторами “рулить”.

А вообще CoolRuner это классическая Альтеровская PLD-ха.

В 90-х Альтера продала свою технологию Филипсу, те ,надо отдать должное, здорово снизили потребление, но продукт массовости не получил.

Xilinx же PLD так и не научился делать( хотя с FPGA у него все нормально) просто перекупает все подразделение, и теперь делает нормальные PLD как и Альтера.

P.S. CoolRuner - Филипсовское название.

Примерно так. Осталось запаять пару перемычек и прошить CPLD. И можно тестировать.

ждем с нетерпением тестов…

В лоб не прокомпилилась, там используется Ксайлинкоская либа, но у Альтеры есть аналогичная - попробую ее прикрутить.

Похоже дело в распиновке ног на OSCA, OSCB и CLK. Разместил ноги:

CLK - P1

OSCA - P42

OSCB - P2

Теперь ругается только на CLK и похоже требует чтобы я ей схему включения CLK нарисовал.

Cpld - Inferring BUFG constraint for signal ‘CLK’ based upon the LOC constraint ‘P1’. It is recommended that you declare this BUFG explicitedly in your design. Note that for certain device families the output of a BUFG constraint can not drive a gated clock, and the BUFG constraint will be ignored.

В общем дело в распиновке. Читаю документацию.

Этот пип ПЛД требует подключения CLK на выделенный (по доке) пин - нуна назначить на него и подключить входной буффер.

Ну и какой это пин и как подключить входной буффер?

Спаял сегодня программатор. Пока сверлил плату сломал два сверла 😦 Грустно.

Перенес в проекте OSCA с 44 на 42 ногу (CLK и OSCB остались на старых 2 и 43) и все ошибки ушли. Подключил праграмматор через LPT кабель. Провозился с пару часов но так законнектится к CPLD не смог. Все проверил, даже саму CPLD на другую перепаял, не помогло. Потом выяснил что по умолчанию iMPACT использует Parallel Cable IV а у меня III. Поменял настройки, не помогло. Выкинул нахрен кабель и воткнул программатор напрямую в LPT порт. Все заработало как часы. Значит надо поиграться с входными сопротивлениями в программаторе.

CPLD прошилась быстро и после перегрузки питания получил красивые ипмульсы CLK (OSCB-).

Теперь вторая проблемма. Моя покупная плата опторазвязки наотрез отказывается работать с частотами сигналов STEP. DIR проходит а ШАГ проскочить не успевает. Оптопары стоят 817D. На самом драйвере опторазвязка отсутствует, а напрямую в LPT порт (даже для теста) подсоединять что-то страшновато. Придется завтра паять опторазвязку на HCPL2631.

при использовании Мача можно инвертануть сигнал степ - полегчает.

тут подробно с картинками как настроить мач kosmodrom.com.ua/data/cncstepdriver/cnccall.php