5-Microstep Drive. Xilinx CPLD

По поводу перегрева. Можно генерить сигнал estop. Станок останавливается. Ничего не теряется. Зато спасаются драйверы и двигателя (их тоже можно мониторить). Есть работы которые требуют от станка 5-8-10 часов непрерывной работы. Будете все это время стоять и смотреть как оно там трудится? А если вентилятор переклинит, мотор уйдет в недопостимо горячие режимы, как тогда? Все эти защиты не являются обязательнымми. Но они спасают оборудование.

Конкретно эту логику можно внедрить в станок на ЛЮБОМ контроллере. Притом вариантов решения море: От термореле с выносным датчиком, коих китайцы понаделали море и совсем занедорого до простейшего каскада на оу с небольшой обвеской и термистором.

Всевозможные защиты железа это не самое главное в этом проекте. Это побочные прибамбасы которые помогут сделать жизнь лучше.

Цель сделать 5шаговый, а еще лучше 10 или 16 шаговый режим. Менять шаг в замисимости от оборотов двигателя. С увеличением частоты уходить с микрошага на 1/4 , 1/2 полный шаг. В статье выше написано при каких оборотах куда сваливать. Настройки в Mach менять не надо. Ему только сказать что работаем с 1/8 или 1/16 шага. CPLD в зависимости от оборотов (читай меряем частоту сигналов STEP, а еще точнее количество пульсов CLK между сигналами STEP) будет подставлять в формируемую виртуальную синусоиду нужные значения (мультиплексор управляемый счетчиком частоты STEP). На выходе должна получаться синусоида при малом шаге и прямоугольник при полном (или что-то около того). ШИМ при этом работает без изменений. При отсутствии сигналов STEP более 1сек (детектор сделан железно на заряде-разряде RC цепочки) выдается 71% или около того от полного тока двигателя. Почти все основные функции уже сделаны Марисом. Надо лишь “расширить” функциональность (как например изменение микрошага). CPLD нужно брать что-то из серии XC2C64A-7VQ44C. В два раза больше микроячеек и побольше портов ввода/вывода. Габариты ненамного больше а расстояние между выводами 0.8мм что вполне приемлимо для домашних плат. У Марисса на этом чипе (только может другой корпус) сделан его 203V драйв со всеми этими фишками плюс защита от короткого замыкания обмотки двигателя на корпус и переполюсовка питания. Каким-то образом это работает через обычный предохранитель но силовые транзисторы выгореть не успевают.

Есть счастливые обладатели Geckodrive? Можете плату отсканировать с обеих сторон чтобы рассмотреть как там защита устроена (у него плата 4-х слойная). Наверняка там кроме предохранителей еще что-то воткнуто. Уж очень хочется “подсмотреть” краешком глаза “как там у них” это работает.

Неужели никому не интересно, или дальше интереса дело не идет?

Ветераны общения с XILINX молчат, может начинающие смогут закрутить это колесо? Как только я доведу до ума свой LS7290 тогда вплотную этим и займусь.

XC2C32 изначально заложенная в этот проект заведомо недостаточна для реализации того, о чем вы говорите. Она применима только в варианте “побаловаться” с шаговиками. По поводу шага выводов и домашних условий- делать плату контроллера чпу сколь нибудь умного в домашних условиях по меньшей мере непонятное занятие, по простой причине. Развести нормально плату с плисиной и силовой частью для такого контроллера в один слой сможет только профи экстра класса и то с вероятностью 60-70 процентов, во всех остальных случаях такая плата будет серьезно ухудшать потребительские свойсва. Т.е опять же возврашяемся к тому что домашняя плата разумна только в варианте “поиграться с шаговиками”. Я несколько лет назад тоже делал платы под плиски сам. Но сейчас жалею, что тратил время на упихивание всего на 1 слой.

adgd.ru/images/img_oscill_05.jpg

adgd.ru/images/img_oscill_06.jpg

Офтоп: это Вы делали осциллограф?

Ветераны общения с XILINX молчат, может начинающие смогут закрутить это колесо? Как только я доведу до ума свой LS7290 тогда вплотную этим и займусь.

Мы весной плотно обсуждали этот проект, я даже модельнул его на Альтере,

но LS7290 на мой взгляд более подходит.

… Менять шаг в замисимости от оборотов двигателя. С увеличением частоты уходить с микрошага на 1/4 , 1/2 полный шаг. В статье выше написано при каких оборотах куда сваливать. Настройки в Mach менять не надо…

Вы несколько неправильно поняли картинки Марисса.

Смысл его затеи в том, что

- степень дробления шага (1/N) не меняется, она const, полный шаг ШД при любой скорости состоит из N импульсов STEP;

- при изменении частоты STEP происходит только трансформация формы опорного напряжения.

Что это значит на практике:

- при низкой частоте STEP опорное напряжение по форме SIN;

- в переходной зоне частот STEP, опорное напряжение - искаженный (как бы ограниченный по амплитуде, с мягким ограничением) SIN;

- при высокой скорости STEP опорное по форме - трапеция (практически прямоугольник).

Это хорошо видно по осциллограммам Марисса.

Реализацию этого на BascomAVR можно посмотреть в проекте Mardus-Kreutz для униполярного драйвера, там в таблицах форм хорошо все видно и сделано почти как у Марисса.

Мы весной плотно обсуждали этот проект, я даже модельнул его на Альтере,

но LS7290 на мой взгляд более подходит.

Да, мне интересно было попробовать ПЛМ, спасибо Юрий, еще раз.

Только до практике дело так и не дошло: другие проблемы больше занимают, а начинать серьезное дело ради 2,3,4 драйверов для себя… Уже куража не хватает, сдулся.

Всем спасибо.

Проект можно считать похороненным. Дитя умерло так и не успев родиться 😦

Проект можно считать похороненным. Дитя умерло так и не успев родиться

Это еще почему?

Да как-то не движется.

Сегодня послал запрос в avnet.com, может подкинут сэмплов для комплектации на один драйв для начала.

Сэмплов не подкинули, пришлось накупить рассыпухи вместе с XC2C64A-7VQ44C. теперь надо плату под это дело ваять. Схему обвязки наверно надо брать вот отсюда. Она мне почему-то больше нравится. И у меня такое ощущение что она очень близка к реальной схеме драйвера G203V.

Марисс говорит что для связки IR2104 + IRF540N резисторы в цепи затвора не нужны, и если внимательно посмотреть на фотографию G250 на сайте geckodrives.com то там видно прямое соединение с затворами IRF540N. Кто что думает по этому поводу?

Все детали приехали. Можно строить драйвер. Осталось только плату развести, с моими темпами это получится не скоро.

Что-то никак не могу разобраться как в Xilinx ISE 10.1.03 программу скомпилировать и через JTAG записать в CPLD. Кто нибудь может просветить?

Для заливки отдельная тулза. Programmer чего-то там. Воопщем после компиляции нужно указать какие чипы есть в JTAG цепочке, задать для каждого чипа файл выхода и влить его, но перед тем еще нужно имплементировать то, что ты хочешь в этот чип и провести финальную симуляцию, уже на уровне кристалла, с проверкой выдерживания таймингов. Впринципе на сайте xilinx есть отличные мануалы, в частности по CPLD к родной отладке есть довольно увесистая книжечка в деталях описывающая процесс.

impact должна называться

хотя может еще как то переименовали

www.xilinx.com/support/…/xapp069.pdf

Народ, приветик.

Вижу, многие мучаются с программированием Xilinx. Я в свое время тоже разбирался в этой проблеме, так что делюсь своим опытом. Просмотрите приложенный файл - это часть выполненного курсовика по Verilog, железо от Digilent - тестовая плата со Спартаном-3. Курсовик выполнен как пошаговая инструкция по программированию.

Народ, приветик.

Просмотрите приложенный файл

Ну и куда смотреть? Где файл потерялся?

файл с описанием

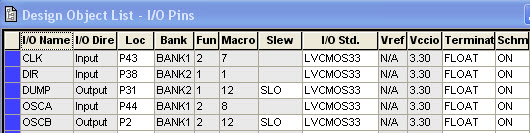

CPLD Xilinx CoolrunnerII, XC2C64-7VQ44C

После компиляции проекта выходит два предупреждения:

[Warning]:INFO:Cpld - Inferring BUFG constraint for signal ‘CLK’ based upon the LOC constraint ‘P43’. It is recommended that you declare this BUFG explicitedly in your design. Note that for certain device families the output of a BUFG constraint can not drive a gated clock, and the BUFG constraint will be ignored.INFO:Cpld - Inferring BUFG constraint for signal ‘OSCA’ based upon the LOC constraint ‘P44’. It is recommended that you declare this BUFG explicitedly in your design. Note that for certain device families the output of a BUFG constraint can not drive a gated clock, and the BUFG constraint will be ignored.

[Warning]:Cpld:1239 - The global clock designation (BUFG) on signal ‘OSCA_IBUF’ is ignored. Most likely the signal is gated and therefore cannot be used as a global control signal.

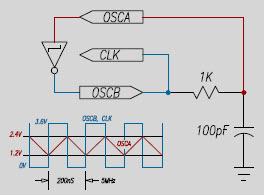

Схема внешнего генератора простая:

Соответственно ноги в Floorplan IO

Строка в Verilog описывающая эту функцию: assign OSCB = ~OSCA;

Что это за BUFG constraint и где ее надо правильно описать?

Пришли проект, попробую в Максе-Квартусе откомпилить.

А можно это в Алтеру перекомпилять ?

А можно это в Алтеру перекомпилять ?

ЛЕГКО!

ЛЕГКО!

Насколько я помню, Марисс там активно использует выходы с открытым коллектором. В дешевых Альтерах они тоже есть?

P.S. Я то сам так и не сподобился двинуться дальше баловства, суета сует…