5-Microstep Drive. Xilinx CPLD

Ветераны общения с XILINX молчат, может начинающие смогут закрутить это колесо? Как только я доведу до ума свой LS7290 тогда вплотную этим и займусь.

Мы весной плотно обсуждали этот проект, я даже модельнул его на Альтере,

но LS7290 на мой взгляд более подходит.

… Менять шаг в замисимости от оборотов двигателя. С увеличением частоты уходить с микрошага на 1/4 , 1/2 полный шаг. В статье выше написано при каких оборотах куда сваливать. Настройки в Mach менять не надо…

Вы несколько неправильно поняли картинки Марисса.

Смысл его затеи в том, что

- степень дробления шага (1/N) не меняется, она const, полный шаг ШД при любой скорости состоит из N импульсов STEP;

- при изменении частоты STEP происходит только трансформация формы опорного напряжения.

Что это значит на практике:

- при низкой частоте STEP опорное напряжение по форме SIN;

- в переходной зоне частот STEP, опорное напряжение - искаженный (как бы ограниченный по амплитуде, с мягким ограничением) SIN;

- при высокой скорости STEP опорное по форме - трапеция (практически прямоугольник).

Это хорошо видно по осциллограммам Марисса.

Реализацию этого на BascomAVR можно посмотреть в проекте Mardus-Kreutz для униполярного драйвера, там в таблицах форм хорошо все видно и сделано почти как у Марисса.

Мы весной плотно обсуждали этот проект, я даже модельнул его на Альтере,

но LS7290 на мой взгляд более подходит.

Да, мне интересно было попробовать ПЛМ, спасибо Юрий, еще раз.

Только до практике дело так и не дошло: другие проблемы больше занимают, а начинать серьезное дело ради 2,3,4 драйверов для себя… Уже куража не хватает, сдулся.

Всем спасибо.

Проект можно считать похороненным. Дитя умерло так и не успев родиться 😦

Проект можно считать похороненным. Дитя умерло так и не успев родиться

Это еще почему?

Да как-то не движется.

Сегодня послал запрос в avnet.com, может подкинут сэмплов для комплектации на один драйв для начала.

Сэмплов не подкинули, пришлось накупить рассыпухи вместе с XC2C64A-7VQ44C. теперь надо плату под это дело ваять. Схему обвязки наверно надо брать вот отсюда. Она мне почему-то больше нравится. И у меня такое ощущение что она очень близка к реальной схеме драйвера G203V.

Марисс говорит что для связки IR2104 + IRF540N резисторы в цепи затвора не нужны, и если внимательно посмотреть на фотографию G250 на сайте geckodrives.com то там видно прямое соединение с затворами IRF540N. Кто что думает по этому поводу?

Все детали приехали. Можно строить драйвер. Осталось только плату развести, с моими темпами это получится не скоро.

Что-то никак не могу разобраться как в Xilinx ISE 10.1.03 программу скомпилировать и через JTAG записать в CPLD. Кто нибудь может просветить?

Для заливки отдельная тулза. Programmer чего-то там. Воопщем после компиляции нужно указать какие чипы есть в JTAG цепочке, задать для каждого чипа файл выхода и влить его, но перед тем еще нужно имплементировать то, что ты хочешь в этот чип и провести финальную симуляцию, уже на уровне кристалла, с проверкой выдерживания таймингов. Впринципе на сайте xilinx есть отличные мануалы, в частности по CPLD к родной отладке есть довольно увесистая книжечка в деталях описывающая процесс.

impact должна называться

хотя может еще как то переименовали

www.xilinx.com/support/…/xapp069.pdf

Народ, приветик.

Вижу, многие мучаются с программированием Xilinx. Я в свое время тоже разбирался в этой проблеме, так что делюсь своим опытом. Просмотрите приложенный файл - это часть выполненного курсовика по Verilog, железо от Digilent - тестовая плата со Спартаном-3. Курсовик выполнен как пошаговая инструкция по программированию.

Народ, приветик.

Просмотрите приложенный файл

Ну и куда смотреть? Где файл потерялся?

файл с описанием

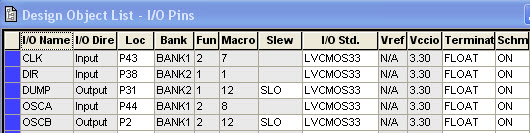

CPLD Xilinx CoolrunnerII, XC2C64-7VQ44C

После компиляции проекта выходит два предупреждения:

[Warning]:INFO:Cpld - Inferring BUFG constraint for signal ‘CLK’ based upon the LOC constraint ‘P43’. It is recommended that you declare this BUFG explicitedly in your design. Note that for certain device families the output of a BUFG constraint can not drive a gated clock, and the BUFG constraint will be ignored.INFO:Cpld - Inferring BUFG constraint for signal ‘OSCA’ based upon the LOC constraint ‘P44’. It is recommended that you declare this BUFG explicitedly in your design. Note that for certain device families the output of a BUFG constraint can not drive a gated clock, and the BUFG constraint will be ignored.

[Warning]:Cpld:1239 - The global clock designation (BUFG) on signal ‘OSCA_IBUF’ is ignored. Most likely the signal is gated and therefore cannot be used as a global control signal.

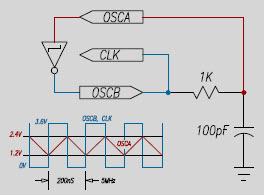

Схема внешнего генератора простая:

Соответственно ноги в Floorplan IO

Строка в Verilog описывающая эту функцию: assign OSCB = ~OSCA;

Что это за BUFG constraint и где ее надо правильно описать?

Пришли проект, попробую в Максе-Квартусе откомпилить.

А можно это в Алтеру перекомпилять ?

А можно это в Алтеру перекомпилять ?

ЛЕГКО!

ЛЕГКО!

Насколько я помню, Марисс там активно использует выходы с открытым коллектором. В дешевых Альтерах они тоже есть?

P.S. Я то сам так и не сподобился двинуться дальше баловства, суета сует…

Насколько я помню, Марисс там активно использует выходы с открытым коллектором. В дешевых Альтерах они тоже есть?

А кто мешает верхний транзистор закрыть ПОСТОЯННО?

Чего там нет, так это триггера шмидта по входу, но генераторы и на простых входах стабильно работают.

ЛЕГКО!

Пожалуйста. Просто Алтер на списанных\дохлых платах завались. а Ксилинков обыскался.

А кто мешает верхний транзистор закрыть ПОСТОЯННО?

Чего там нет, так это триггера шмидта по входу, но генераторы и на простых входах стабильно работают.

Юрий, Вы на этом деле стаю собак уже съели 😃, а для меня это новость, что можно раздельно управлять плечами выходного каскада.

Там есть даже “примитив” opndrn - сам все делает, но если есть желание то можно и по отдельности транзисторами “рулить”.

А вообще CoolRuner это классическая Альтеровская PLD-ха.

В 90-х Альтера продала свою технологию Филипсу, те ,надо отдать должное, здорово снизили потребление, но продукт массовости не получил.

Xilinx же PLD так и не научился делать( хотя с FPGA у него все нормально) просто перекупает все подразделение, и теперь делает нормальные PLD как и Альтера.

P.S. CoolRuner - Филипсовское название.